我們說看到的大部分單片機,基本都實現(xiàn)了內(nèi)部集成電路(I2C)串行總線接口。I2C對于連接主板或嵌入式系統(tǒng)上的許多低速外設非常有用。這些接口使用7位尋址方案,它允許多個主設備通過簡單的2線總線控制多個外設。

在設計PCB時,有時由于總線的物理尺寸變得很大,因此需要緩沖器。I2C緩沖器就像一種中繼器,但它并不意味著克服總線上的損耗。由于I2C總線的上升時間通常較慢,因此這些總線不會像高速數(shù)字總線那樣因損耗而出現(xiàn)信號衰減。相反,它們將時序特性恢復到某個所需的水平,以便可以根據(jù)需要使總線的大小更大。

一、I2C總線電氣特性

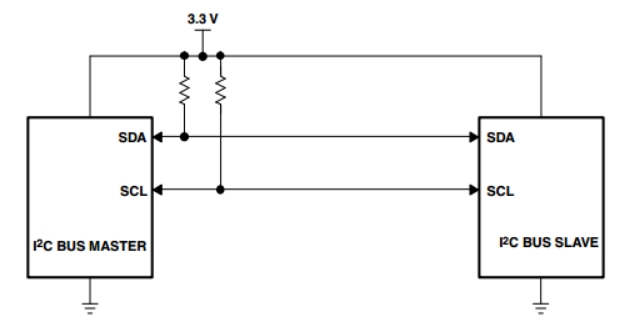

I2C總線由兩條活動線組成:串行時鐘(SCL)和串行數(shù)據(jù)(SDA)線。這兩條線都連接到主控制器或外圍ASIC上的引腳,這兩個引腳都是需要上拉電阻的開漏引腳。這意味著主設備或外圍設備可以將SDA線拉低,而上拉電阻器被動地將線返回到高電壓電平,從而切換所有邏輯狀態(tài)。

影響I2C總線性能的兩個關(guān)鍵電氣參數(shù)包括:

(1)總線電容(Cbus):SCL和SDA跡線以及連接到總線的設備上的所有輸入引腳的電容較高,會增加數(shù)據(jù)信號和時鐘沿的上升時間。

(2)上拉電阻(R):SCL/SDA和VCC之間連接一個電阻。較低的電阻值會縮短上升時間,但會增加流經(jīng)開漏極的電流(功耗較高)。

I2C總線中上拉電阻的典型值為10 kOhms。例如,如果總總線電容為 100 pF,則SCL/SDA信號的 10%-90%上升時間約為2.2微秒。通過將I2C總線本質(zhì)上視為充電/放電RC電路,可以輕松計算出這一點。總線如下圖所示:

隨著越來越多的設備添加到I2C總線,由于每個設備的負載電容和額外的走線電容,Cbus的值也會增加。最終,總電容將降低可以可靠支持的最大I2C時鐘速度。較高的總線電容可以用較小的上拉電阻來抵消,但較小的電阻會通過開漏引腳增加功耗。有些漏極電流可能僅限于幾毫安,這就是上拉電阻值應在10 kOhms左右的原因。

如果上升時間超過I2C器件的輸入閾值區(qū)域,緩慢的上升時間也會導致時序問題,這可能會導致接口時序窗口期間電壓電平的錯誤。

為什么要添加I2C緩沖器?

為了說明為什么需要I2C緩沖器,讓我們考慮一個例子。假設我們有一塊帶有兩個I2C設備、一個單片機和一個EEPROM的板。單片機充當I2C主設備,EEPROM充當外圍設備。

在400 kHz的快速模式時鐘速度下,主機可以正確地訪問EEPROM中的數(shù)據(jù),不會出現(xiàn)時序錯誤。但如果在板上添加更多外圍 IC,總線最終會停止工作。這些額外的設備增加了現(xiàn)有總線的電容。由于這些設備全部并行添加到總線,因此增加的電容開始導致總線上所有設備的上升時間變慢,并最終出現(xiàn)通信錯誤。

解決I2C總線性能限制的主要方法有幾種:

(1)較低的上拉電阻值:使用較小的電阻可縮短上升時間,但會因增加漏極電流而大大增加功耗。

(2)降低I2C時鐘速度:這會增加SCL/SDA信號上升沿的時序裕度,但也會降低吞吐量。

(3)添加I2C緩沖器/中繼器:I2C緩沖器將總線分成多個較小的段,這些段可以通過緩沖器獨立驅(qū)動。

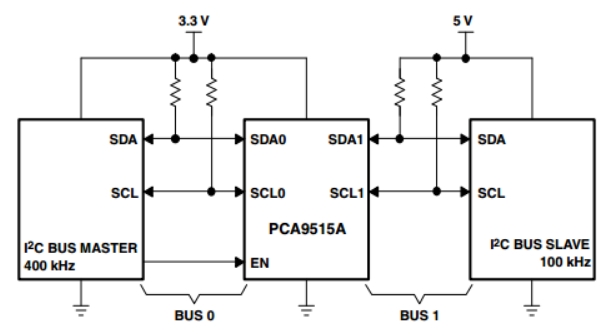

I2C緩沖器及其總線連接的結(jié)構(gòu)如下所示:

二、在PCB設計中實現(xiàn)I2C緩沖器

I2C緩沖器允許工程師將大型總線劃分為較小的段,這最大限度地減少了每個部分的電容。通過降低電容,可以增加上拉電阻值以降低I2C功耗,同時仍滿足上升時間要求。

I2C緩沖器還可以提供電平轉(zhuǎn)換功能,可在段之間升高或降低信號。這允許高壓設備與低壓設備通信,但兩個電源電壓都需要添加到PCB中。

設計PCB時,如果出現(xiàn)以下情況,請考慮添加I2C緩沖器或中繼器:

(1)I2C總線具有來自許多設備的高電容。

(2)由于上拉電阻較大,SDA/SCL上升時間太慢。

(3)I2C設備需要不同的信號電平。

(4)I2C設備需要不同的時鐘頻率。

(5)I2C器件具有不同的上拉電阻限制。

(6)總線速度較高時會發(fā)生通信錯誤。

使用I2C緩沖器的一些好處包括:

(1)將大總線分成更小的段以減少電容。

(2)通過最小化每個段上的電阻值來延長上升時間。

(3)與單個長總線相比,可實現(xiàn)更高的I2C時鐘速度。

(4)防止傳播延遲影響總線時序。

(5)隔離總線段之間的電氣噪聲。

三、I2C緩沖器的放置位置

當布局具有多個I2C設備的PCB時,有幾種有效的方法來放置I2C緩沖器:

(1)將設備集群分成I2C段。如果某些 I2C 設備在電路板上物理分組在一起,則在集群之間放置緩沖器可將它們隔離到單獨的總線段中。這包含每組內(nèi)的電容。

(2)將緩沖器放置在總線中間附近。在長總線的中間放置緩沖器有助于在兩個段上均勻地分配電容。這樣,緩沖器在總線的每一側(cè)看到/創(chuàng)建相似的上升時間。

(3)在電容非常高的設備附近放置一個緩沖器。如果一些外圍設備具有較大的電容,則可以將它們放置在緩沖器的輸出側(cè),這樣它們就不會減慢總線的其余部分。

(4)使用多個級聯(lián)緩沖器來劃分復雜的總線。對于在大面積上分布有許多設備的總線,級聯(lián)2-3個緩沖器將總線分成幾個低電容段,以獲得更好的性能。

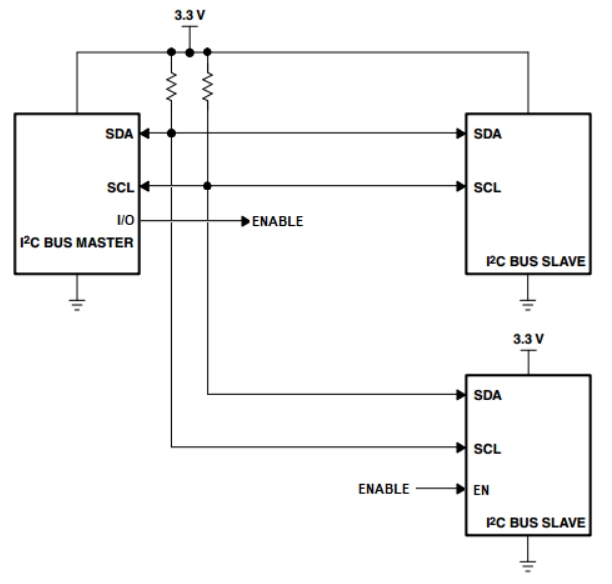

I2C緩沖器作為備份總線

使用 I2C 緩沖器的另一種選擇是作為備份總線,這實際上創(chuàng)建了主設備可以通過其進行通信的冗余總線。如果總線上有可能發(fā)生故障,則可以啟用緩沖器以打開備份組件或外設。這種類型的系統(tǒng)常見于高可靠性應用,例如基礎設施或工業(yè)系統(tǒng)的電力電子設備。

當設備故障可能導致整個系統(tǒng)癱瘓時,就會使用緩沖器。總線上單個設備的故障可以通過在總線上放置一個用緩沖器分隔的冗余電路來克服。然后可以通過打開其電源或切換其ENABLE/SHDN引腳來啟用緩沖器。

在這種情況下,需要一種控制方法來感測受保護設備并確定該設備是否發(fā)生故障。如果設備發(fā)生故障,主控制器可以通過切換使能引腳切換到受保護的總線。這需要在嵌入式應用中多付出一些功夫,但考慮余量來設計總線可確保系統(tǒng)的長期可靠性。

以上就是英銳恩單片機開發(fā)工程師分享的單片機PCB電路設計知識:為I2C總線添加緩沖器。英銳恩專注單片機應用方案設計與開發(fā),提供8位單片機、32位單片機。